**TC530**

**TC534**

## 5V PRECISION DATA ACQUISITION SUBSYSTEMS

#### **FEATURES**

- Precision (up to 17 Bits) A/D Converter

- 3 Wire Serial Port

- Flexible: User Can Trade-Off Conversion Speed Against Resolution

- Single Supply Operation

- -5V Output Pin

- 4 Input, Differential Analog MUX (TC534)

- Automatic Input Polarity and Overrange Detection

- Low Operating Current ...... 5mA Max

- Wide Analog Input Range ..... ±4.2V Max

- Cost Effective

#### ORDERING INFORMATION

| Part No. | Package                       | Temp. Range  |

|----------|-------------------------------|--------------|

| TC530COI | 28-Pin SOIC                   | 0°C to +70°C |

| TC530CPJ | 28-Pin Plastic DIP (300 Mil.) | 0°C to +70°C |

| TC534CKW | 44-Pin PQFP                   | 0°C to +70°C |

| TC534CPL | 40-Pin Plastic DIP            | 0°C to +70°C |

| TC530EV  | Evaluation Kit for TC530/5    | 34           |

#### **GENERAL DESCRIPTION**

The TC530/534 are serial analog data acquisition subsystems ideal for high precision measurements (up to 17 bits plus sign). The TC530 consists of a dual slope integrating A/D converter, negative power supply generator and 3 wire serial interface port. The TC534 is identical to the TC530, but adds a four channel differential input multiplexer. Key A/D converter operating parameters (Auto Zero and Integration time) are programmable, allowing the user to trade-off conversion time for resolution.

Data conversion is initiated when the RESET input is brought low. After conversion, data is loaded into the output shift register and EOC is asserted indicating new data is available. The converted data (plus Overrange and polarity bits) is held in the output shift register until read by the processor, or until the next conversion is completed allowing the user to access data at any time.

The TC530/534 timebase can be derived from an external crystal of 2MHz (max), or from an external frequency source. The TC530/534 requires a single 5V power supply and features a - 5V, 10mA output which can be used to supply negative bias to other components in the system.

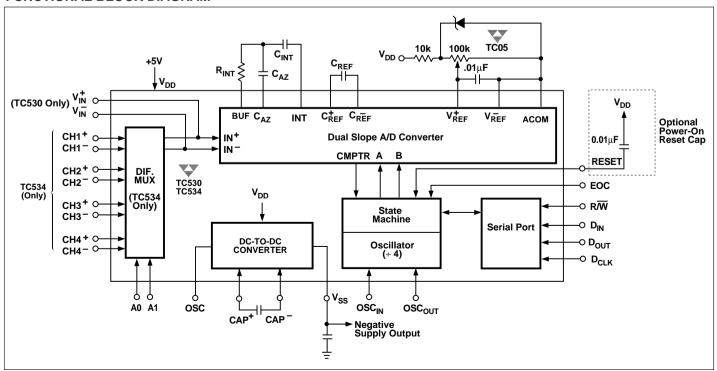

#### **FUNCTIONAL BLOCK DIAGRAM**

## TC530 TC534

### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage                                             | +6V                                |

|------------------------------------------------------------|------------------------------------|

| Analog Input Voltage (V <sub>IN</sub> or V <sub>IN</sub> ) | V <sub>DD</sub> to V <sub>SS</sub> |

| Logic Input Voltage(V <sub>DD</sub> + 0                    |                                    |

| Ambient Operating Temperature Ran                          | ige                                |

| Plastic DIP Package                                        | (C)                                |

| 0°C to +70°C                                               |                                    |

| SOIC Package (C)                                           | 0°C to +70°C                       |

| PQFP Package (C)                                           | 0°C to +70°C                       |

| Storage Temperature Range                                  | 65°C to +150°C                     |

| Lead Temperature (Soldering, 10 sec).                      | +300°C                             |

\*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**ELECTRICAL CHARACTERISTICS**

|                     |                                                    |                         | T <sub>A</sub> = +25° | $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |     |     |     |     |      |

|---------------------|----------------------------------------------------|-------------------------|-----------------------|--------------------------------------|-----|-----|-----|-----|------|

| Symbol              | Parameter                                          | Test Conditions         | Min                   | Тур                                  | Max | Min | Тур | Max | Unit |

| $\overline{V_{DD}}$ | Analog Power Supply Voltage                        |                         | 4.5                   | 5.0                                  | 5.5 | 4.5 | _   | 5.5 | V    |

| $V_{CCD}$           | Digital Power Supply Voltage                       |                         | 4.5                   | 5.0                                  | 5.5 | 4.5 | _   | 5.5 | V    |

| P <sub>D</sub>      | TC530/534 Total Power Dissipation                  | $V_{DD} = V_{CCD} = 5V$ | _                     | _                                    | 25  | _   | _   | _   | mW   |

| Is                  | Supply Current (V <sub>S</sub> + P <sub>IN</sub> ) |                         | _                     | 1.8                                  | 2.5 | _   | _   | 3.0 | mA   |

| I <sub>CCD</sub>    | Supply Current (V <sub>CCD</sub> P <sub>IN</sub> ) | f <sub>OSC</sub> = 1MHz | _                     | _                                    | 1.5 | _   | _   | 1.7 | mA   |

## **ELECTRICAL CHARACTERISTICS:** $V_{DD} = V_{CCD}$ , $C_{AZ} = C_{REF} = 0.47 \mu F$ , unless otherwise specified.

|                     |                                              |                                       | TA                    | = +25°( | C                     | $T_A = 0$             |       |                       |        |

|---------------------|----------------------------------------------|---------------------------------------|-----------------------|---------|-----------------------|-----------------------|-------|-----------------------|--------|

| Symbol              | Parameter                                    | Test Conditions                       | Min                   | Тур     | Max                   | Min                   | Тур   | Max                   | Unit   |

| Analog              |                                              |                                       |                       |         |                       |                       |       |                       |        |

| R                   | Resolution                                   | Note 1                                | _                     | -       | ±17                   | _                     | _     | ±17                   | Bits   |

| ZSE                 | Zero-Scale Error<br>with Auto Zero Phase     | _                                     | _                     | 0.5     | _                     | 0.005                 | 0.012 | % F.S.                |        |

| ENL                 | End Point Linearity                          | Note 1 and 2                          | _                     | 0.015   | 0.030                 | _                     | 0.015 | 0.045                 | % F.S. |

| NL                  | Max Deviation from Best<br>Straight Line Fit | Notes 1 and 2                         | _                     | 0.008   | 0.015                 | _                     | _     | _                     | % F.S. |

| ZS <sub>TC</sub>    | Zero-Scale Temperature<br>Coefficient        |                                       | _                     | _       | _                     | _                     | 1     | 2                     | μV/°C  |

| SYE                 | Roll-Over Error                              | Note 3                                | _                     | .012    | _                     | _                     | .03   | _                     | % F.S. |

| FS <sub>TC</sub>    | Full-Scale Temperature<br>Coefficient        | Ext. V <sub>REF</sub><br>TC = 0ppm/°C | _                     | _       | _                     | _                     | 10    | _                     | ppm/°C |

| I <sub>IN</sub>     | Input Current                                | $V_{IN} = 0V$                         | _                     | 6       | _                     | _                     | _     | _                     | pА     |

| V <sub>CMR</sub>    | Common-Mode<br>Voltage Range                 |                                       | V <sub>SS</sub> + 1.5 | _       | V <sub>DD</sub> – 1.5 | V <sub>SS</sub> + 1.5 | _     | V <sub>DD</sub> – 1.5 | V      |

| V <sub>INT</sub>    | Integrator Output Swing                      |                                       | V <sub>SS</sub> + 0.9 | _       | V <sub>DD</sub> - 0.9 | $V_{SS} + 0.9$        | _     | V <sub>DD</sub> - 0.9 | V      |

| $\overline{V_{IN}}$ | Analog Input Signal Range                    |                                       | V <sub>SS</sub> + 1.5 | _       | V <sub>DD</sub> – 1.5 | V <sub>SS</sub> + 1.5 | _     | V <sub>DD</sub> - 1.5 | V      |

| $V_{REF}$           | Voltage Reference Range                      |                                       | V <sub>SS</sub> + 1   | _       | V <sub>DD</sub> – 1   | V <sub>DD</sub> + 1   | _     | $V_{DD} - 1$          | V      |

| $t_D$               | Zero Crossing Comparator                     |                                       |                       | 2.0     |                       |                       | 3.0   | _                     | μsec   |

#### **ELECTRICAL CHARACTERISTICS:**

**Serial Port Interface:** V<sub>CCD</sub> = +5V, unless otherwise specified.

|                     |                                           |                          | $T_A = +25^{\circ}C$ |     |     | $T_A = 0$ |     |      |      |

|---------------------|-------------------------------------------|--------------------------|----------------------|-----|-----|-----------|-----|------|------|

| Symbol              | Parameter                                 | Test Conditions          | Min                  | Тур | Max | Min       | Тур | Max  | Unit |

| $\overline{V_{IH}}$ | Input Logic HIGH Level                    |                          | 2.5                  | _   | _   | 2.5       | _   | _    | V    |

| $V_{IL}$            | Input Logic LOW Level                     |                          | _                    | _   | 0.8 | _         | _   | 0.8  | V    |

| I <sub>IN</sub>     | Input Current (DI, DO, D <sub>CLK</sub> ) |                          | _                    | _   | 10  | _         | _   | _    | μА   |

| V <sub>OL</sub>     | Logic LOW Output Voltage (EOC)            | I <sub>OUT</sub> = 250μA | _                    | 0.2 | 0.3 | _         | _   | 0.35 | V    |

#### **ELECTRICAL CHARACTERISTICS:**

**Serial Port Interface:** V<sub>CCD</sub> = +5V, unless otherwise specified.

|                  |                                            | T <sub>A</sub> = +25°C |     |     | $T_A = 0^{\circ}C$ to $+70^{\circ}C$ |     |     |     |      |

|------------------|--------------------------------------------|------------------------|-----|-----|--------------------------------------|-----|-----|-----|------|

| Symbol           | Parameter                                  | Test Conditions        | Min | Тур | Max                                  | Min | Тур | Max | Unit |

| tR, tF           | Rise and Fall Times<br>(EOC, DI, DO)       | C <sub>L</sub> = 10pF  | _   | _   | 250                                  | _   | 250 | _   | nsec |

| F <sub>XTL</sub> | Crystal Frequency                          |                        | _   | _   | 2.0                                  | _   | _   | 2.0 | MHz  |

| F <sub>EXT</sub> | External Frequency on OSC <sub>IN</sub>    |                        | _   | _   | 4.0                                  | _   | _   | 4.0 | MHz  |

| t <sub>RS</sub>  | Read Setup Time                            |                        | 1   | _   | _                                    | _   | 1   | _   | μsec |

| t <sub>RD</sub>  | Read Delay Time                            |                        | 250 | _   | _                                    | _   | 250 | _   | nsec |

| t <sub>DRS</sub> | D <sub>CLK</sub> to D <sub>OUT</sub> Delay |                        | 450 | _   | _                                    | _   | 450 | _   | nsec |

| t <sub>PWL</sub> | D <sub>CLK</sub> LOW Pulse Width           |                        | 150 | _   | _                                    | _   | 150 | _   | nsec |

| t <sub>PWH</sub> | D <sub>CLK</sub> HIGH Pulse Width          |                        | 150 | _   | _                                    | _   | 150 | _   | nsec |

| $t_{DR}$         | Data Ready Delay                           |                        | 200 | _   | _                                    | _   | 200 | _   | nsec |

#### **ELECTRICAL CHARACTERISTICS:**

**DC/DC Converter Section:** V<sub>DD</sub> = +5V, unless otherwise specified.

|                  |                                |                         | Т   | T <sub>A</sub> = +25°C |     |     | $T_A = 0^{\circ}C \text{ To } +70^{\circ}C$ |     |      |  |

|------------------|--------------------------------|-------------------------|-----|------------------------|-----|-----|---------------------------------------------|-----|------|--|

| Symbol           | Parameter                      | Test Conditions         | Min | Тур                    | Max | Min | Тур                                         | Max | Unit |  |

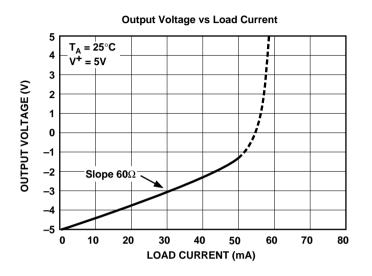

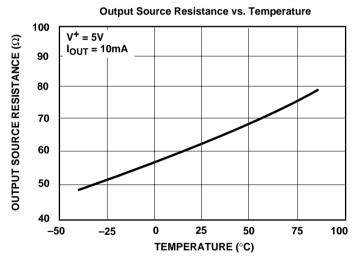

| R <sub>OUT</sub> | Output Resistance              | I <sub>OUT</sub> = 10mA | _   | 65                     | 85  | _   | _                                           | 100 | Ω    |  |

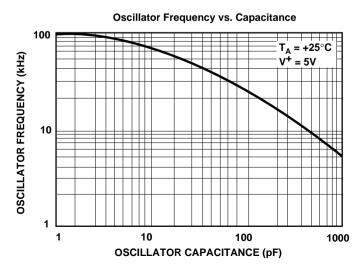

| f <sub>CLK</sub> | Oscillator Frequency           | $C_{OSC} = 0$           | _   | 100                    | _   | _   | _                                           | _   | kHz  |  |

| I <sub>OUT</sub> | V <sub>SS</sub> Output Current |                         | _   | _                      | 10  | _   | _                                           | 10  | mA   |  |

#### **ELECTRICAL CHARACTERISTICS:**

Multiplexer: V<sub>DD</sub> = +5V (Note 4), unless otherwise specified.

|                    |                            | T <sub>A</sub> = +25°C |       |     | $T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ |      |     |     |      |

|--------------------|----------------------------|------------------------|-------|-----|---------------------------------------------|------|-----|-----|------|

| Symbol             | Parameter                  | Test Conditions        | Min   | Тур | Max                                         | Min  | Тур | Max | Unit |

| V <sub>INMAX</sub> | Maximum Input Voltage      |                        | - 2.5 | _   | 2.5                                         | -2.5 | _   | 2.5 | V    |

| R <sub>DSON</sub>  | Drain/Source ON Resistance |                        | _     | 6   | 10                                          | _    | _   | _   | kΩ   |

**Notes:** 1. Integrate time  $\geq$  66msec, Auto Zero time  $\geq$  66msec,  $V_{INT}$  (pk) = 4V.

- 2. End point linearity at  $\pm 1/4$ ,  $\pm 1/2$ ,  $\pm 3/4$  F.S. after full scale adjustment.

- 3. Roll-over error is related to capacitor used for  $C_{INT}$  (See "Recommended Suppliers for  $C_{INT}$ ", Table 2).

- 4. TC534 Only.

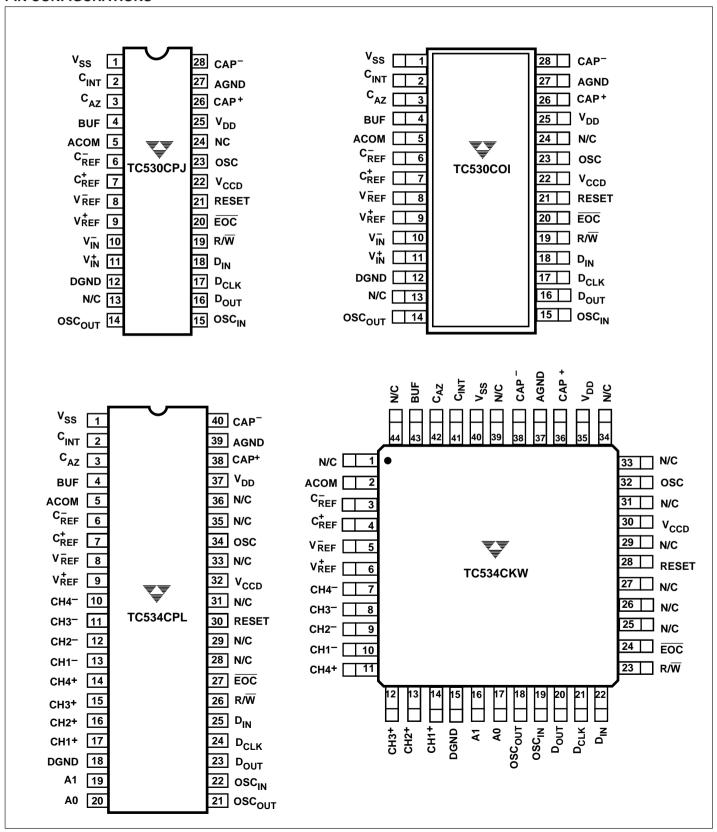

#### **PIN CONFIGURATIONS**

## **5V PRECISION DATA ACQUISITION SUBSYSTEMS**

**TC530** TC534

## **PIN DESCRIPTION**

| Pin No.<br>(TC530<br>28-Pin<br>PDIP, 300 Mil | Pin No.<br>(TC530<br>28-Pin<br>I.) SOIC) | Pin No<br>(TC534<br>40-Pin<br>PDIP) | Pin No.<br>(TC534<br>44-Pin<br>PQFP) | Symbol              | Description                                                                                                                                                                                                                                                                                |

|----------------------------------------------|------------------------------------------|-------------------------------------|--------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                            | 1                                        | 1                                   | 40                                   | V <sub>SS</sub>     | Analog Output. Negative power supply converter output and reservoir capacitor connection. This output can be used to provide negative bias to other devices in the system.                                                                                                                 |

| 2                                            | 2                                        | 2                                   | 41                                   | C <sub>INT</sub>    | Analog Output. Integrator capacitor connection and integrator output.                                                                                                                                                                                                                      |

| 3                                            | 3                                        | 3                                   | 42                                   | C <sub>AZ</sub>     | Analog Input. Auto Zero capacitor connection.                                                                                                                                                                                                                                              |

| 4                                            | 4                                        | 4                                   | 43                                   | BUF                 | Analog Output. Integrator capacitor connection and voltage buffer output.                                                                                                                                                                                                                  |

| 5                                            | 5                                        | 5                                   | 2                                    | ACOM                | Analog Input. This pin is ground for all of the analog switches in the A/D converter. It is grounded for most applications. ACOM and the input common pin $(V_{\text{IN}} \text{ or } \text{Chx}^-)$ should be within the common mode range, CMR.                                          |

| 6                                            | 6                                        | 6                                   | 3                                    | $C_REF^-$           | Analog Input. Reference cap negative connection.                                                                                                                                                                                                                                           |

| 7                                            | 7                                        | 7                                   | 4                                    | C <sub>REF</sub>    | Analog Input. Reference cap positive connection.                                                                                                                                                                                                                                           |

| 8                                            | 8                                        | 8                                   | 5                                    | $V_{REF}^-$         | Analog Input. External voltage reference negative connection                                                                                                                                                                                                                               |

| 9                                            | 9                                        | 9                                   | 6                                    | $V_{REF}^{\dagger}$ | Analog Input. External voltage reference positive connection.                                                                                                                                                                                                                              |

| Not Used                                     | Not Used                                 | 10                                  | 7                                    | CH4 <sup>-</sup>    | Analog Input. Multiplexer channel 4 negative differential analog input.                                                                                                                                                                                                                    |

| Not Used                                     | Not Used                                 | 11                                  | 8                                    | CH3 <sup>-</sup>    | Analog Input. Multiplexer channel 3 negative differential analog input.                                                                                                                                                                                                                    |

| Not Used                                     | Not Used                                 | 12                                  | 9                                    | CH2 <sup>-</sup>    | Analog Input. Multiplexer channel 2 negative differential analog input.                                                                                                                                                                                                                    |

| Not Used                                     | Not Used                                 | 13                                  | 10                                   | CH1 <sup>-</sup>    | Analog Input. Multiplexer channel 1 negative differential analog input.                                                                                                                                                                                                                    |

| Not Used                                     | Not Used                                 | 14                                  | 11                                   | CH4+                | Analog Input. Multiplexer channel 4 positive differential analog input.                                                                                                                                                                                                                    |

| Not Used                                     | Not Used                                 | 15                                  | 12                                   | CH3 <sup>+</sup>    | Analog Input. Multiplexer channel 3 positive differential analog input.                                                                                                                                                                                                                    |

| Not Used                                     | Not Used                                 | 16                                  | 13                                   | CH2 <sup>+</sup>    | Analog Input. Multiplexer channel 2 positive differential analog input.                                                                                                                                                                                                                    |

| Not Used                                     | Not Used                                 | 17                                  | 14                                   | CH1 <sup>+</sup>    | Analog Input. Multiplexer channel 1 positive differential analog input.                                                                                                                                                                                                                    |

| 10                                           | 10                                       | Not Used                            | Not Used                             | VīN                 | Analog Input. Negative differential analog voltage input.                                                                                                                                                                                                                                  |

| 11                                           | 11                                       | Not Used                            | Not Used                             | V <sub>IN</sub>     | Analog Input. Positive differential analog voltage input.                                                                                                                                                                                                                                  |

| 12                                           | 12                                       | 18                                  | 15                                   | DGND                | Analog Input. Ground connection for serial port circuit.                                                                                                                                                                                                                                   |

| Not Used                                     | Not Used                                 | 19                                  | 16                                   | A1                  | Logic Level Input. Multiplexer address MSB.                                                                                                                                                                                                                                                |

| Not Used                                     | Not Used                                 | 20                                  | 17                                   | A0                  | Logic Level Input. Multiplexer address LSB.                                                                                                                                                                                                                                                |

| 14                                           | 14                                       | 21                                  | 18                                   | OSC <sub>OUT</sub>  | Analog Input. Timebase for state machine. This pin connects to one side of an AT-cut crystal having an effective series resistance of $100\Omega$ (typ) and a parallel capacitance of $20pF$ If an external frequency source is used to clock the TC530/53 this pin must be left floating. |

## 5V PRECISION DATA ACQUISITION SUBSYSTEMS

## TC530 TC534

## PIN DESCRIPTION (Cont.)

| Pin No.<br>(TC530<br>28-Pin<br>PDIP, 300 Mil.) | Pin No.<br>(TC530<br>28-Pin<br>SOIC) | Pin No<br>(TC534<br>40-Pin<br>PDIP) | Pin No.<br>(TC534<br>44-Pin<br>PQFP) | Symbol            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------|--------------------------------------|-------------------------------------|--------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15                                             | 15                                   | 22                                  | 19                                   | OSC <sub>IN</sub> | Analog Input. This pin connects to the other side of the crystal described in OSC <sub>OUT</sub> above. The TC530/534 may also be clocked from an external frequency source connected to this pin. The external frequency source must be a pulse wave form with a minimum 30% duty cycle and rise and fall times 15nsec (Max). If an external frequency source is used, OSC <sub>OUT</sub> must be left floating. A maximum operating frequency of 2MHz (crystal) or 4MHz (external clock source) is permitted. |

| 16                                             | 16                                   | 23                                  | 20                                   | D <sub>OUT</sub>  | Logic Level Output. Serial port data output pin. This pin is enabled only when $R/\overline{W}$ is high.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17                                             | 17                                   | 24                                  | 21                                   | D <sub>CLK</sub>  | Logic Input, Positive and Negative Edge Triggered. Serial port clock. When R/ $\overline{W}$ is high, serial data is clocked out of the TC530/534A (on D <sub>OUT</sub> ) at each HIGH-to-LOW transition of D <sub>CLK</sub> . A/D initialization data (LOAD VALUE) is clocked into the TC530/534 (on D <sub>IN</sub> ) at each LOW-to-HIGH transition of D <sub>CLK</sub> . A maximum serial port D <sub>CLK</sub> frequency of 3MHz is permitted.                                                             |

| 18                                             | 18                                   | 25                                  | 22                                   | D <sub>IN</sub>   | Logic Level Input. Serial port input pin. The A/D converter integration time ( $T_{INT}$ ) and Auto Zero time ( $T_{AZ}$ ) values are determined by the LOAD VALUE byte clocked into this pin. This initialization must take place at power up, and can be rewritten (or modified and rewritten) at any time. The LOAD VALUE is clocked into D <sub>IN</sub> MSB first.                                                                                                                                         |

| 19                                             | 19                                   | 26                                  | 23                                   | R/W               | Logic Level Input. This pin must be brought low to perform a write to the serial port (e.g. initialize the A/D converter). The D <sub>OUT</sub> pin of the serial port is enabled only when this pin is high.                                                                                                                                                                                                                                                                                                   |

| 20                                             | 20                                   | 27                                  | 24                                   | EOC               | Open Drain Output. End-of-Conversion (EOC) is asserted any time the TC530/534 is in the AZ phase of conversion. This occurs when either the TC530/534 initiates a normal AZ phase, or when RESET is pulled high. EOC is returned high when the TC530/534 exits AZ. Since EOC is driven low immediately following completion of a conversion cycle, it can be used as a DATA READY processor interrupt.                                                                                                          |

| 21                                             | 21                                   | 30                                  | 28                                   | RESET             | Logic Level Input. It is necessary to force the TC530/534 into the Auto Zero phase when power is initially applied. This is accomplished by momentarily taking RESET high. Using an I/O port line from the microprocessor, or by applying an external system reset signal, or by connecting a $0.01\mu F$ capacitor from the RESET input to $V_{SS}$ .                                                                                                                                                          |

|                                                |                                      |                                     |                                      |                   | Conversions are performed continuously as long as RESET is low and conversion is halted when RESET is high. RESET may therefore be used in a complex system to momentarily suspend conversion (for example while the address lines of an input multiplexer are changing state). In this case, RESET should be pulled high only when the $\overline{EOC}$ is LOW to avoid excessively long integrator discharge times which could result in erroneous conversion (see <i>Applications</i> Section).              |

## PIN DESCRIPTION (Cont.)

| Pin No.<br>(TC530<br>28-Pin<br>PDIP, 300 Mil.) | Pin No.<br>(TC530<br>28-Pin<br>SOIC) | Pin No<br>(TC534<br>40-Pin<br>PDIP) | Pin No.<br>(TC534<br>44-Pin<br>PQFP)        | Symbol           | Description                                                                                                                                                                                                                                     |

|------------------------------------------------|--------------------------------------|-------------------------------------|---------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22                                             | 22                                   | 32                                  | 30                                          | V <sub>CCD</sub> | Analog Input. Power supply connection for digital logic and serial port. Proper power-up sequencing is critical, see the <i>Applications</i> section.                                                                                           |

| 23                                             | 23                                   | 34                                  | 32                                          | OSC              | Input. The negative power supply converter normally runs at a frequency of 100kHz. This frequency can be slowed down to reduce quiescent current by connecting an external capacitor between this pin and V\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| 25                                             | 25                                   | 37                                  | 35                                          | $V_{DD}$         | Analog Input. Power supply connection for the A/D analog section and DC-DC converter. Proper power-up sequencing is critical, see the <i>Applications</i> section.                                                                              |

| 26                                             | 26                                   | 38                                  | 36                                          | CAP+             | Analog Input. Storage capacitor positive connection for the DC/DC converter.                                                                                                                                                                    |

| 27                                             | 27                                   | 39                                  | 37                                          | AGND             | Analog Input. Ground connection for DC/DC converter.                                                                                                                                                                                            |

| 28                                             | 28                                   | 40                                  | 38                                          | CAP-             | Analog Input. Storage capacitor negative connection for the DC/DC converter.                                                                                                                                                                    |

| 13, 24                                         | 13, 24                               | 28, 29, 31,<br>33, 35, 36           | 1, 25, 26, 27<br>29, 31, 33,<br>34, 39, 44, | NC               | No connect. Do not connect any signal to these pins.                                                                                                                                                                                            |

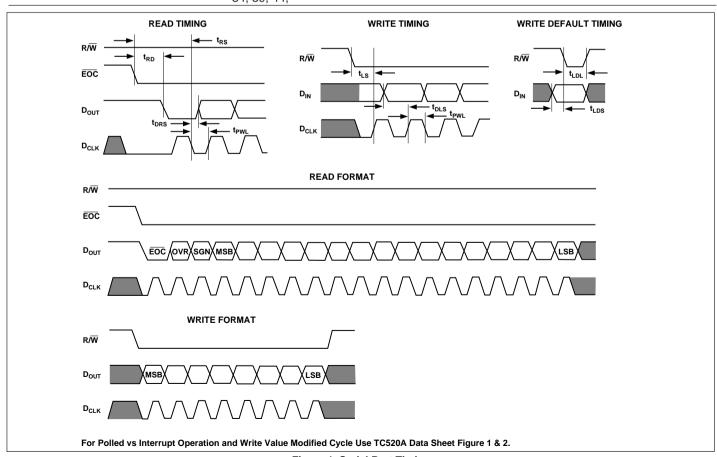

Figure 1. Serial Port Timing

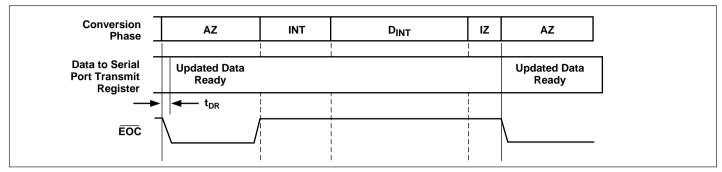

Figure 2. A/D Converter Timing

# DETAILED DESCRIPTION Dual Slope Integrating Converter

The TC530/534 dual slope converter operates by integrating the input signal for a fixed time period, then applying an opposite polarity reference voltage while timing the period (counting clocks pulses) for the integrator output to cross 0V (deintegrating). The resulting count is read as conversion data.

A simple mathematical expression that describes dual slope conversion is:

(1) Integrate Voltage = Deintegrate Voltage

(2)

$$1/R_{INT}C_{INT}$$

$$\begin{cases} t_{INT} \\ V_{IN}(t)dt = 1/R_{INT}C_{INT} \\ 0 \end{cases} V_{REF}$$

from which:

$$(3) \ (\mathsf{V}_\mathsf{IN}) \left[ \frac{(\mathsf{t}_\mathsf{INT})}{(\mathsf{R}_\mathsf{INT})(\mathsf{C}_\mathsf{INT})} \right] = (\mathsf{V}_\mathsf{REF}) \left[ \frac{(\mathsf{t}_\mathsf{DINT})}{(\mathsf{R}_\mathsf{INT})(\mathsf{C}_\mathsf{INT})} \right]$$

and therefore:

(4)

$$V_{IN} = V_{REF} \left[ \frac{t_{DINT}}{t_{INT}} \right]$$

where:  $V_{REF}$  = Reference Voltage  $t_{INT}$  = Integrate Time

t<sub>DINT</sub> = Reference Voltage Deintegrate Time

Inspection of equation (4) shows dual slope converter accuracy is unrelated to integrating resistor and capacitor values, as long as they are stable throughout the measurement cycle. This measurement technique is inherently ratiometric (i.e., the ratio between the  $t_{\text{INT}}$  and  $t_{\text{DINT}}$  times is equal to the ratio between  $V_{\text{IN}}$  and  $V_{\text{REF}}$ ).

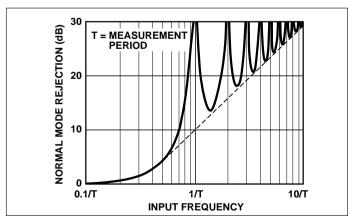

Another inherent benefit is noise immunity. Input noise spikes are integrated (or averaged to zero) during the integration period. The integrating converter has a noise immunity with an attenuation rate of at least –20dB per decade. Interference signals with frequencies at integral multiples of the integration period are, for the most part, completely removed. For this reason, the integration period of the converter is often established to reject 50/60Hz line noise. The ability to reject such noise is shown by the plot of Figure 3.

In addition to the two phases required for dual slope measurement (Integrate and Deintegrate), the TC530/534 performs two additional adjustments to minimize measurement error due to system offset voltages. The resulting four internal operations (conversion phases) performed each measurement cycle are: Auto Zero (AZ), Integrator Output Zero (IZ), Input Integrate (INT) and Reference Deintegrate (DINT). The AZ and IZ phases compensate for system offset errors and the INT and DINT phases perform the actual A/D conversion.

Figure 3. Integrating Converter Normal Mode Rejection

## **5V PRECISION DATA ACQUISITION SUBSYSTEMS**

**TC530 TC534**

#### Auto Zero Phase (AZ)

This phase compensates for errors due to buffer, integrator and comparator offset voltages. During this phase, an internal feedback loop forces a compensating error voltage on auto zero capacitor (CAZ). The duration of the AZ phase is programmable via the serial port (see also Programming AZ and INT Phase Duration paragraph of this document).

### Input Integrate Phase (INT)

In this phase, a current directly proportional to differential input voltage is sourced into integrating capacitor C<sub>INT</sub>. The amount of voltage stored on C<sub>INT</sub> at the end of the INT phase is directly proportional to the applied differential input voltage. Input signal polarity (sign bit) is determined at the end of this phase. Converter resolution and conversion speed is a function of the duration of the INT phase, which is programmable by the user via the serial port (see also Programming AZ and INT Phase Duration paragraph of this document). The shorter the integration time, the faster the speed of conversion, but the lower the resolution. Conversely, the longer the integration time, the greater the resolution, but at slower the speed of conversion.

#### Reference Deintegrate Phase (DINT)

This phase consists of measuring the time for the integrator output to return (at a rate determined by the external reference voltage) from its initial voltage to 0V. The resulting timer data is stored in the output shift register as converted analog data.

#### Integrator Output Zero Phase (IZ)

This phase guarantees the integrator output is at zero volts when the AZ phase is entered so that only true system offset voltages will be compensated for.

All internal converter timing is derived from the frequency source at OSC<sub>IN</sub> and OSC<sub>OUT</sub>. This frequency source must be either an externally provided clock signal, or an external crystal. If an external clock is used, it must be connected to the OSCIN pin and the OSCOUT pin must remain floating. If a crystal is used, it must be connected between OSC<sub>IN</sub> and OSC<sub>OUT</sub> and physically located as close to the OSC<sub>IN</sub> and OSC<sub>OUT</sub> pins as possible. In either case, the incoming clock frequency is divided by four and the resulting clock serves as the internal TC530/534 timebase.

#### **APPLICATIONS**

### Programming the TC530/534

#### AZ and INT Phase Duration:

These two phases have equal duration determined by the crystal (or external) frequency and the timer initialization byte (LOAD VALUE). Timing is selected as follows:

#### (1) Select Integration Time

Integration time must be picked as a multiple of the period of the line frequency. For example, t<sub>INT</sub> times of 33msec, 66msec and 132msec maximize 60Hz line rejection.

#### (2) Estimate Crystal Frequency

Crystal frequencies as high as 2MHz are allowed. Crystal frequency is estimated using:

$$\begin{split} F_{IN} &= \frac{2(R)}{t_{INT}} \\ \text{where:} \ R &= \text{Desired Converter Resolution} \\ &\quad \text{(in counts)} \\ F_{IN} &= \text{Input Frequency (in MHz)} \\ INT &= \text{Integration Time (in seconds)} \end{split}$$

#### (3) Calculate LOAD VALUE

[LOAD VALUE]<sub>10</sub> =

$$256 - \frac{(t_{INT})(F_{IN})}{1024}$$

F<sub>IN</sub> can be adjusted to a standard value during this step. The resulting base -10 LOAD VALUE must be converted to a hexadecimal number, then loaded into the serial port prior to initiating A/D conversion.

#### **DINT** and IZ Phase Timing

The duration of the D<sub>INT</sub> phase is a function of the amount of voltage stored on the integrator capacitor during INT, and the value of V<sub>REF</sub>. The D<sub>INT</sub> phase is initiated immediately following INT and terminated when an integrator output zero-crossing is detected. In general, the maximum number of counts chosen for D<sub>INT</sub> is twice that of INT (with  $V_{REF}$  chosen at  $V_{IN}(max)/2$ ).

#### **System RESET**

The TC530/534 must be forced into the AZ state when power is first applied. A .01µF capacitor connected from RESET to V<sub>CC</sub> (or external system reset logic signal) can be used to momentarily drive RESET high for a minimum of 100msec.

## Selecting Component Values for the TC530/534

#### (1) Calculate Integrating Resistor (R<sub>INT</sub>)

The desired full-scale input voltage and amplifier output current capability determine the value of R<sub>INT</sub>. The buffer and integrator amplifiers each have a fullscale current of 20µA.

The value of R<sub>INT</sub> is therefore directly calculated as follows:

$$R_{INT}(M\Omega) = \frac{V_{INMAX}}{20}$$

where:  $V_{INMAX} = Maximum Input Voltage (full count)$

voltage)

$R_{INT}$  = Integrating Resistor (in  $M\Omega$ )

For loop stability,  $R_{INT}$  should be  $\geq 50k\Omega$ .

## (2) Select Reference ( $C_{REF}$ ) and Auto Zero ( $C_{AZ}$ ) Capacitors

$C_{REF}$  and  $C_{AZ}$  must be low leakage capacitors (such as polypropylene). The slower the conversion rate, the larger the value  $C_{REF}$  must be. Recommended capacitors for  $C_{REF}$  and  $C_{AZ}$  are shown in Table 1. Larger values for  $C_{AZ}$  and  $C_{REF}$  may also be used to limit roll-over errors.

Table 1. C<sub>REF</sub> and C<sub>AZ</sub> Selection

| Conversions<br>Per Second | Typical Value of C <sub>REF</sub> , C <sub>AZ</sub> (μF) | Suggested * Part Number |

|---------------------------|----------------------------------------------------------|-------------------------|

| >7                        | 0.1                                                      | WIMA MK12 .1/63/20      |

| 2 to 7                    | 0.22                                                     | WIMA MK12 .22/63/20     |

| 2 or less                 | 0.47                                                     | WIMA MK12 .47/63/20     |

<sup>\*</sup>WIMA Corp. listing on the last page of this data sheet.

#### 3. Calculate Integrating Capacitor (C<sub>INT</sub>)

The integrating capacitor must be selected to maximize integrator output voltage swing. The integrator output voltage swing is defined as the absolute value of  $V_{DD}$  (or  $V_{SS}$ ) less 0.9V (i.e.  $|V_{DD}-0.9V|$  or  $|V_{SS}+0.9V|$ ). Using the 20µA buffer maximum output current, the value of the integrating capacitor is calculated using the following equation:

$$C_{INT}(\mu F) = \frac{(t_{INT})(20)}{(V_S - 0.9)}$$

where:  $t_{INT}$  = Integration Period

$V_S$  = Applied Supply Voltage

$C_{INT}$  = Integrator Capacitor Value (in  $\mu F$ )

It is critical that the integrating capacitor have a very low dielectric absorption. PPS capacitors are an example of one such chemistry. Table 2 summarizes various capacitors suitable for  $C_{\mathsf{INT}}$ .

Table 2. Recommend Capacitor for CINT

| Value | Suggested Part Number* |

|-------|------------------------|

| 0.1   | WIMA MK12 .1/63/20     |

| 0.22  | WIMA MK12 .22/63/20    |

| 0.33  | WIMA MK12 .33/63/20    |

| 0.47  | WIMA MK12 .47/63/20    |

<sup>\*</sup>WIMA Corp. listing on the last page of this data sheet.

#### 4. Calculate V<sub>RFF</sub>

The reference deintegration voltage is calculated using:

$$V_{REF} (in Volts) = \frac{(V_S - 0.9)(C_{INT})(R_{INT})}{2(t_{INT})}$$

#### **Serial Port**

Communication with the TC530/534 is accomplished over a 3 wire serial port. Data is clocked into  $D_{IN}$  on the rising edge of  $D_{CLK}$  and clocked out of  $D_{OUT}$  on the falling edge of  $D_{CLK}$ . R/W must be HIGH to read converted data from the serial port and LOW to write the LOAD VALUE to the TC530/534.

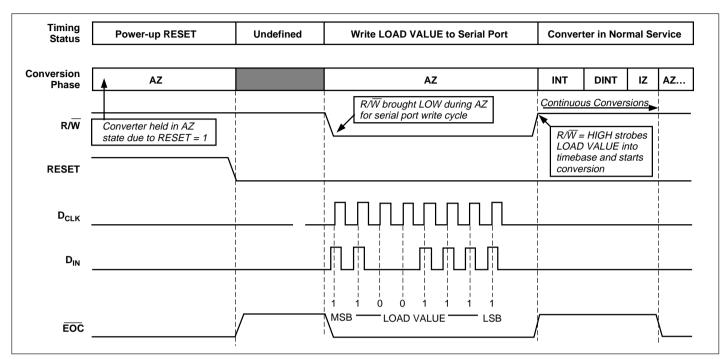

#### Load Value Write Cycle (Figure 4)

Following the power-up reset pulse, the LOAD VALUE (which sets the duration of AZ and INT) must next be transmitted to the serial port. To accomplish this, the processor monitors the state of  $\overline{EOC}$  (which is available as a hardware output or at  $D_{OUT}$ ). R/W is taken low to initiate the write cycle only when  $\overline{EOC}$  is low (during the AZ phase). (Failure to observe  $\overline{EOC}$  low may cause an offset voltage to be developed across  $C_{INT}$  resulting in erroneous readings). The 8 bit LOAD VALUE data on  $D_{IN}$  is clocked in by  $D_{CLK}$ . The processor then terminates the write cycle by taking R/W high. (Data is transferred from the serial input shift register to the time base counter on the rising edge of R/W, and data conversion is initiated).

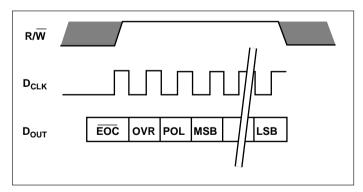

#### Data Read Cycle (Figure 5)

Data is shifted out of the serial port in the following order: End of Conversion ( $\overline{EOC}$ ), Overrange (OVR), Sign (SGN), conversion data (MSB first). When R/W is high, the state of the  $\overline{EOC}$  bit can be polled by simply reading the state of D<sub>OUT</sub>. This allows the processor to determine if new data is available without connecting an additional wire to the  $\overline{EOC}$  output pin (this is especially useful in a polled environment).

#### Input Multiplexer (TC534 Only)

A 4 input, differential multiplexer is included in the TC534. The states of channel address lines A0 and A1 determine which differential V<sub>IN</sub> pair is routed to the con-

Figure 4. TC530/534 Initialization and Load Value Write Cycle

verter input. A0 is the least significant address bit (i.e., channel 1 is selected when A0 = 1 and A1 = 0). The multiplexer is designed to be operated in a differential mode. For single-ended inputs, the CHx input for the channel under selection must be connected to the ground reference associated with the input signal.

Figure 5. Serial Port Data Read Cycle

#### **DC/DC Converter**

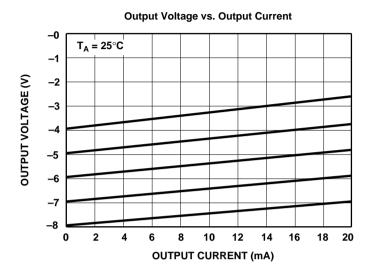

An on-board, TC7660H-type charge pump supplies negative bias to the converter circuitry, as well as to external devices. The charge pump develops a negative output voltage by moving charge from the power supply to the reservoir capacitor at VSS by way of the commutating capacitor connected to the CAP+ and CAP- inputs.

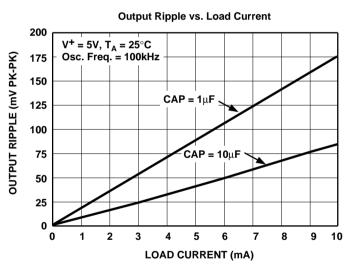

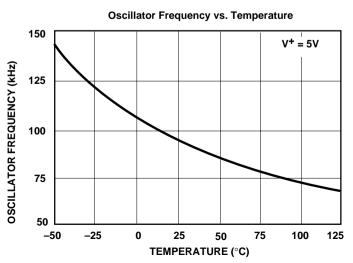

The charge pump clock operates at a typical frequency of 100kHz. If lower quiescent current is desired, the charge pump clock can be slowed by connecting an external capacitor from the OSC pin to V<sub>DD</sub>. Reference typical characteristics curves.

#### **APPLICATIONS**

#### Design Example

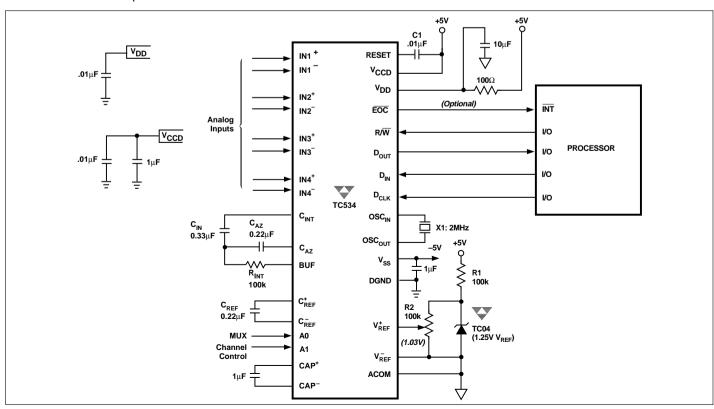

Figure 6 shows a typical TC534 interrupt-driven application. Timing and component values are calculated from equations and recommendations made in the Dual Slope Integrating Converter and Programming the TC530/534 sections of this document. The EOC connection to the processor INT input is for interrupt-driven applications only. (In polled systems, the EOC output is available on  $D_{OUT}$ ).

#### **GIVEN**

REQUIRED RESOLUTION: 16 Bits (65,536 counts.)

MAXIMUM V<sub>IN</sub>: POWER SUPPLY VOLTAGE: +5V 60Hz SYSTEM

1. Pick Integration time (t<sub>INT</sub>) 66msec

2. Estimate crystal frequency

$F_{IN} = 2R/t_{INT} = 2 \times 65536/66 \times 10^{-3} = 1.98MHz$ (use 2MHz)

## TC530 TC534

#### 3. Calculate LOAD VALUE

LOAD VALUE =  $256 - (t_{INT})(F_{IN})/1024 = [128]_{10}$  $[128]_{10} = 80 \text{ hex}$

#### 4. Calculate RINT

$R_{INT}$  (in  $M\Omega$ ) =  $V_{INMAX}/20 = 2/20 = 100k\Omega$

## Calculate C<sub>INT</sub> for maximum (4V) integrator output swing

$$C_{INT}$$

(in  $\mu$ F) = ( $t_{INT}$ )(20 x 10  $^{-6}$ )/ ( $V_S$  - 0.9)

= (.066)(20 x 10  $^{-6}$ )/(4.1)

= .32 $\mu$ F (use closest value: 0.33 $\mu$ F)

NOTE: TelCom recommended capacitor: WIMA p/n: MK12 .33/63/10

#### 6. Choose C<sub>REF</sub> and C<sub>AZ</sub> based on conversion rate

Conversions/sec=

$$1/(t_{AZ} + t_{INT} + 2t_{INT} + 2msec)$$

=  $1/(66msec + 66msec + 132msec + 2msec)$

=  $3.7$  conversions/sec

from which  $C_{AZ} = C_{REF} = 0.22 \mu F$  (see Table 1)

NOTE: TelCom recommended capacitor: WIMA p/n: MK12 .22/63/10

#### 7. Calculate V<sub>REF</sub>

$$V_{REF} \text{ (in Volts } = (V_S - 0.9)(C_{INT})(R_{INT})$$

$$= \frac{2(t_{INT})}{(4.1)(0.33 \times 10^{-6})(10^5)/2(.066)}$$

$$= 1.025 \text{ V}$$

### **Power Supply Sequencing**

Improper sequencing of the power supply inputs (V<sub>DD</sub> vs. V<sub>CCD</sub>) can potentially cause an improper power-up sequence to occur. See *Circuit Design/Layout Considerations* below. Failing to insure a proper power-up sequence can cause spurious operation.

### **Ciruit Design/Layout Considerations**

(1) Separate ground return paths should be used for the analog and digital circuitry. Use of ground planes and trace fill on analog circuit sections is highly recommended EXCEPT for in and around the integrator section and  $C_{REF}$ ,  $C_{AZ}$ ,  $(C_{INT}$ ,  $C_{REF}$ ,  $C_{AZ}$ ,  $R_{INT}$ ). Stray capacitance between these nodes and ground appears in parallel with the components themselves and can affect measurement accuracy.

Figure 6. TC530/534 Typical Application

## 5V PRECISION DATA ACQUISITION SUBSYSTEMS

## TC530 TC534

- (2) Improper sequencing of the power supply inputs  $(V_{DD} \, vs. \, V_{CCD})$  can potentially cause an improper power-up sequence to occur in the internal state machines. It is recommended that the digital supply,  $V_{CCD}$ , be powered up first. One method of insuring the correct power-up sequence is to delay the analog supply using a series resistor and a capacitor. See Figure 6, TC530/534 Typical Application.

- (3) Decoupling capacitors, preferably a higher value electrolytic or tantulum in parallel with a small ceramic or tantalum, should be used liberally. This includes bypassing the supply connections of all active components and the voltage reference.

- (4) Critical components should be chosen for stability and low noise. The use of a metal-film resistor for  $R_{INT}$  and Polypropylene or Polyphenelyne Sulfide (PPS) capacitors for  $C_{INT}$ ,  $C_{AZ}$ , and  $C_{REF}$  is highly recommended.

- (5) The inputs and integrator section are very high impedance nodes. Leakage to or from these critical nodes can contribute measurement error. A guard-ring should be used to protect the integrator section from stray leakage.

- (6) Circuit assemblies should be scrupulously clean to prevent the presence of contamination from assembly, handling, or the cleaning itself. Minutely conductive trace contaminates, easily ignored in most applications, can adversely affect the performance of high impedance circuits. The input and integrator sections should be made as compact and close to the TC53x as possible.

- (7) Digital and other dynamic signal conductors should be kept as far from the TC53x's analog section as possible. The microcontroller or other host logic should be kept quiet during a measurement cycle. Background activites such as keypad scanning, display refreshing, and power switching can introduce noise.

#### **TC530EV Evaluation Kit**

The TC530EV consists of a 4" x 6" pre-assembled circuit board that connects to the serial port of any PC or dumb terminal. Also included is a Windows<sup>TM\*</sup> Excel<sup>TM\*</sup>-based design utility that calculates component and LOAD values based on user input, and prints a finished circuit schematic. Please contact your local TelCom representative for more information, or point your web browser to http://www.telcomsemi.com.

<sup>\*</sup>All trademarks are the property of their respective owners.

### **TYPICAL CHARACTERISTICS**

### WIMA Corporation Capacitor Representatives (Tables 1 and 2)

#### Australia:

#### ADILAM ELECTRONICS (PTY.) LTD.

P.O. Box 664 3 Nicole Close Bayswater 3153 Tel.: 3-7 61 44 66 Fax: 3-7 61 41 61

#### Canada:

#### R-THETA INC.

130 Matheson Blvd. East, Unit 2 Mississauga, Ont. L4Z1Y6 Tel.: 9 05-8 90-02 21 Fax: 9 05-8 90-16 28

## Hong Kong:

#### **REALTRONICS CO. LTD.**

E-3, Hung-On Building 2, King's Road Tel.: 25 70 11 51 Fax: 28 06 84 74

#### **SUSAN AGENCIES**

P.O. Box 2138 Srirampuram P.O. Bangalore-560 021 Tel.: 0 80-3 32 06 62 Fax: 0 80-3 32 43 38

#### Israel:

#### M.G.R. TECHNOLOGY

P.O. Box 2229 Rehavot 76121 Tel.: 9 72-8-41 17 19 Fax: 9 72-8-41 41 78

#### Japan:

#### UNIDUX INC.

5-1-21, Kyonan-Cho Musashino-Shi Tokvo 180 Tel.: 04 22-32-41 11

Fax: 04 22-32-03 31

#### Malaysia:

#### MA ELECTRONICS (M) SDN BHD

346-B Jalan Jelutong 11600 Penang Tel.: 6 04-2 81 45 18 Fax: 6 04-2 81 45 15

#### Singapore:

#### MICROTRONICS ASSOC. (PTE.) LTD.

8, Lorong Bakar Batu 03-01, Kolam Ayer Ind. Park Singapore 1334 Tel.: 65-7 48-18 35

Tlx: 34 929 Fax: 65-7 43-30 65

#### South Africa:

#### KOPP ELECTRONICS LIMITED

P.O. Box 3853 2128 Rivonia Tel.: 0 11-4 44-23 33 Fax: 0 11-4 44-17 06

#### South Korea:

#### YONG JUN ELECTRONIC CO.

#201, Sungwook Bldg. 1460-16, Seocho-Dong Seocho-Ku Seoul, Korea Tel.: 2-52 31 80 02

## Fax: 2-5 23 18 03

#### Taiwan. R.O.C.: SOLOMON TECHNOLOGY CORP.

7th Floor No. 2 Lane 47, Sec. 3 Nan Kang Road Taipei

Tel.: 8 86-2-7 88 89 89 Fax: 8 86-2-7 88 82 75

#### Thailand:

#### MICROTRONICS THAI LTD.

50/68 T.T. Court Cheng Wattana Road Amphur Pak-Kreed Nonthaburi 11120 Tel.: 6 62-5 84 58 07, Ext. 102

Fax: 6 62-5 83 37 75

#### USA:

#### THE INTER-TECHNICAL GROUP, INC. WIMA DIVISION

175 Clearbrook Road P.O. Box 535 Elmsford, NY 10523-0535 Tel.: 914-347-2474 Fax: 914-347-7230

#### TAW ELECTRONICS, INC.

4215, W. Burbank, Blvd. Burbank, CA, 91505 Tel.: 8 18-8 46-39 11 Fax: 8 18-8 46-11 94

#### Venezuela:

#### MAGNETICA. S.A.

Apartado 78117 Caracas 1074 A Tel.: 58-2-2 41 75 09 Fax: 58-2-2 41 55 42